# Spin Valves for Reconfigurable Logic Devices

#### Dissertation

zur Erlangung des Doktorgrades an der MIN-Fakultät, Fachbereich Informatik der Universität Hamburg

vorgelegt von

Bernd Güde aus Buchholz in der Nordheide

Hamburg 2011

Genehmigt von der MIN-Fakultät, Fachbereich Informatik der Universität Hamburg auf Antrag von:

Professor Dr.-Ing. Dietmar P. F. Möller Erstgutachter / Doktorvater

Privatdozent Dr. habil. Guido Meier Zweitgutachter

Professor Dr. Jianwei Zhang Drittgutachter

Hamburg, den 07. Juni 2011

### Abstract

Spin valves are ferromagnetic nanostructures whose electrical resistance can be tuned either by an applied magnetic field, an electrical current, or in combination with an electrical current through thermal excitation. A spin valve consists of at least three layers, two ferromagnetic layers, which are separated by a non-magnetic layer. The electrical resistance of a spin valve depends on the orientation of the magnetization in both ferromagnetic layers. Two configurations are relevant for applications of spin valves in logic and memory devices, parallel and antiparallel alignment of the magnetizations relative to each other. Both correspond to two different resistances, which can represent Boolean values 0 and 1. The electrical resistance of a spin valve can be explained with the giant magnetoresistance (GMR) effect and the tunneling magnetoresistance (TMR) effect, respectively. Spin valves are promising candidates for future logic and memory devices, since they show principle assets compared to traditional technologies based on semiconductor-based field-effect transistors. The technological relevance of spin valves in memory and logic devices and in field-programmable gate arrays is investigated in this work. The acceptability of spin valves for applications is based on models that describe the electrical properties appropriately and efficiently, making spin valve available for circuit designers. Such models are referred to as a compact model. The established model for spin valves, the micromagnetic model, describes the magnetization dynamics in the ferromagnetic layers of the spin valve; it is too generic and not suited for circuit design based on spin valves. In this thesis state-of-the-art compact models for spin valves are reviewed. Following a common approach for compact models in the literature, two different electrical circuits are depicted. Both mimic the most relevant characteristic of a spin valve, the hysteresis of its electrical resistance, but at different levels of abstraction following Gajski and Kuhn's Y chart. The first circuit approximates the hysteresis of a real spin valve, but is simpler than other circuits in the literature. Two case studies indicate the flexibility of the circuit. The feasibility of logic gates based on spin valves is studied employing the circuit and picking up the case studies again. The second circuit allows for the simulation of a spin valve's hysteresis at a tunable precision. The latter circuit is an enhancement compared with recently published works in the literature on the same topic. The circuits were simulated with a free available version of SPICE, the de facto standard for circuit simulation.

### Zusammenfassung

Spinventile sind ferromagnetische Nanostrukturen, deren elektrischer Widerstand mithilfe eines Magnetfeldes, eines elektrischen Stromes oder in Verbindung damit durch Aufheizen eingestellt werden kann. Ein Spinventil besteht wenigstens aus drei Schichten; dabei handelt es sich um zwei ferromagnetische Schichten, die durch eine weitere Schicht getrennt sind. Der elektrische Widerstand eines Spinventils hängt von der Ausrichtung der Magnetisierungen in den ferromagnetischen Schichten ab. Zwei Konfigurationen sind von besonderem Interesse für Anwendungen: Die parallele und antiparallele Ausrichtung der Magnetisierungen zueinander. Beide Konfigurationen führen zu unterschiedlichen Widerständen, mit denen sich die Booleschen Wahrheitswerte 0 und 1 repräsentieren lassen. Der elektrische Widerstand eines Spinventils beruht auf dem gigantischen Magnetwiderstand (GMR) beziehungsweise dem Tunnelmagnetwiderstand (TMR). Spinventile eignen sich besonders für Speicherzellen und Logikgatter, weil sie grundsätzliche Vorteile besitzen im Vergleich zu herkömmlichen Technologien, die auf Halbleiter-Feldeffektransistoren beruhen. In dieser Arbeit wird die technologische Relevanz der Spinventile für Speicherzellen, Logikgatter und Field Programmable Gate Arrays untersucht. Die Akzeptanz von Spinventilen hängt auch von der Verfügbarkeit von Modellen ab, die eine angemessene und einfache Beschreibung ihres Verhaltens erlauben. Diese Modelle erlauben den Entwurf von Schaltungen mit Spinventilen. Einfache, aber angemessene Modelle bezeichnet man als kompakte Modelle. Das gängigste Modell zur Beschreibung eines Spinventils ist das mikromagnetische Modell, das die Dynamik der Magnetisierung in den ferromagnetischen Schichten eines Spinventils beschreibt. Es eignet sich jedoch nicht, um Spinventile für den Schaltungsentwurf zu beschreiben. In dieser Arbeit wird daher der Stand der Technik der kompakten Modelle für Spinventile vorgestellt und bewertet. Einem etablierten Ansatz folgend werden zwei elektrische Ersatzschaltungen vorgestellt. Beide Schaltungen ahmen die für den Schaltungsentwurf wichtigste Eigenschaft eines Spinventils nach. Die Hysterese des Widerstandes wird mit beiden Schaltungen imitiert, allerdings auf verschiedenen Abstraktionsebenen, vergleichbar denen in Gajski und Kuhns Y-Diagramm. Durch die erste Schaltung wird die Hysterese eines Spinventils genähert durch eine rechteckförmige Hysterese. Diese Schaltung ist einfacher als die Arbeiten in der Literatur. Durch zwei Fallstudien wird die Flexibilität der Schaltung deutlich. Damit wird auch die Machbarkeit von Logikgattern untersucht. Die zweite Schaltung erlaubt es, die Hysterese bei einstellbarer Genauigkeit zu simulieren. Diese Schaltung ist eine Weiterentwicklung kürzlich veröffentlichter Arbeiten aus der Literatur. Die Schaltungen wurden mit einer frei verfügbaren Version von SPICE simuliert, dem Standardprogramm zur Schaltungssimulation.

### Contents

| 1            | Introductio                                                        | ntroduction                                                                                                                                      |     |  |  |

|--------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| <b>2</b>     | Fundamentals                                                       |                                                                                                                                                  | 11  |  |  |

|              | 2.1 Historic                                                       | al development                                                                                                                                   | 11  |  |  |

|              | 2.2 Challen                                                        | ges for future devices                                                                                                                           | 12  |  |  |

|              | 2.3 Field-pr                                                       | ogrammable gate arrays based on spin valves                                                                                                      | 18  |  |  |

|              | 2.4 Physics                                                        | of spin valves                                                                                                                                   | 22  |  |  |

|              | 2.5 Modelin                                                        | g and simulation of spin valves                                                                                                                  | 28  |  |  |

| 3            | Compact models for spin valves                                     |                                                                                                                                                  |     |  |  |

|              | 3.1 Compac                                                         | et model for a spin valve with an idealized hysteresis                                                                                           | 36  |  |  |

|              | 3.2 Prototy                                                        | pical implementation of a NAND and a NOR gate using the compact                                                                                  |     |  |  |

|              | model fe                                                           | or the idealized hysteresis                                                                                                                      | 53  |  |  |

|              | 3.3 Compac                                                         | et model for a spin valve with a realistic hysteresis                                                                                            | 64  |  |  |

| 4            | Conclusion                                                         | onclusion and outlook 8                                                                                                                          |     |  |  |

| A            | cknowledgen                                                        | nent                                                                                                                                             | 90  |  |  |

| $\mathbf{A}$ | Netlists of                                                        | the circuits                                                                                                                                     | 93  |  |  |

|              |                                                                    | for the circuit for mimicking spin valves with rectangular hysteresis . for the Wheatstone bridge for measuring the resistance of a field-effect | 94  |  |  |

|              | transiste                                                          | or in its off-state                                                                                                                              | 95  |  |  |

|              | A.3 Netlist                                                        | of the equivalent circuit for logic gates after Richter et al                                                                                    | 96  |  |  |

|              | A.4 Netlist                                                        | of the equivalent circuit for an Ohmic resistor                                                                                                  | 98  |  |  |

|              | A.5 Fit-fund                                                       | tions for the upper and lower branch of the spin valve's hysteresis after                                                                        |     |  |  |

|              | Albert e                                                           | et al                                                                                                                                            | 98  |  |  |

|              | A.6 Netlist                                                        | of the of circuit for a spin valve with a realistic hysteresis                                                                                   | 99  |  |  |

| В            | Contributions to the manuscript "Spin Valves For Innovative Comput |                                                                                                                                                  |     |  |  |

|              | Devices An                                                         | d Architectures"                                                                                                                                 | 102 |  |  |

| $\mathbf{C}$ | Contributio                                                        | Contributions to the manuscript "A Compact Model For Spin Valves in                                                                              |     |  |  |

|              | Computing                                                          | Devices"                                                                                                                                         | 103 |  |  |

#### Contents

| D Other publications / contributions to conferences | 105 |

|-----------------------------------------------------|-----|

| E Research stays                                    | 106 |

| Bibliography                                        |     |

### Chapter 1

### Introduction

Since the invention of the bipolar transistor in 1948, an enormous development in the fabrication of transistors led to a performance hardly anyone could imagine when microelectronics still was in its infancy. Today the semiconductor industry has become a multi-billion dollar business. According to the European Semiconductor Industry Association the worldwide sales in December 2009 for semiconductor devices were raised by 28.9% in comparison to the sales in December 2008 [1]. Innovation is required to maintain such growth rates. Scaling of devices has become an important driver in semiconductor industry. It affects all aspects of a device, like its size or the possible clock rate when switching the device. Scaling cannot be continued forever. Devices cannot get smaller and smaller forever; there are fundamental limits. And even though devices were improved up to now through scaling, some principle drawbacks remain. For example data is accessed very quickly in static random-access memory, but stored only volatile. In common nonvolatile memory technologies, like hard disks data can be accessed only very slowly or the number of write cycles is very limited (e.g. in Flash memory cells). The discovery of the giant magnetoresistance effect in the middle of the 1980's marked the dawn of *spintronics*. In contrast to conventional electronics where the charge of the electron constitutes the state variable, in spintronic devices also the spin degree of freedom is employed to represent the state variable. The technological relevance of spintronic devices is indicated for example by modern hard disks. The read head is a so-called spin valve. A spin valve is a ferromagnetic device of some nanometer in size. It consists of at least three layers, that is, two ferromagnetic layers separated by a non-magnetic layer. The relevant property of any ferromagnet is its magnetization, which can be regarded as the magnetic orientation of a tiny bar magnet. In this principle sketch the whole ferromagnetic layer corresponds to an array of these bar magnets. The magnetization in one layer is fixed, while the other magnetization can be switched with an external magnetic field or an electrical current. For the application of spin valves in electronic systems, two configurations are important: Antiparallel and parallel alignment of the magnetization in the free layer with respect to the other layer, the so-called fixed layer. Both configurations correspond to different electrical resistances. The orientation of the magnetization in both layers remains unchanged in the absence of a magnetic field or a current. The spin valve thus can directly serve as a nonvolatile memory cell. Spin valves can also be employed in logic gates and even in microwave oscillators. Hence, spin valves are

multifunctional devices. The accepted mathematical model for the description of a spin valve is the micromagnetic model. The micromagnetic model describes the magnetization dynamics of the free layer, but does not directly give information about the electrical resistance of the spin valve. For circuit design with spin valves though it is essential to have such a model. Models for the current across the non-magnetic layer have been proposed in the literature [2], but how can the behavior of a spin valve be expressed in the language of a circuit designer? In analogy to the semiconductor field-effect transistor, besides the micromagnetic model another approach for modeling a spin valve is also very popular in the literature: Mimicking the hysteresis of a spin valve with an equivalent electrical circuit. There exists a wide variety of proposals in the literature [3–5]. In this thesis two new equivalent circuits are presented, one that is much simpler than circuits from the literature. The results from simulations using this circuit are very reasonable. The second circuit is also quite simple in its assembly; it can imitate the hysteresis of a spin valve very precisely. The circuit is very flexible, as only the fitting functions and the switching points need to be changed if a different spin valve is to be mimicked. The circuit is almost insensible to loads.

#### This thesis is organized as follows:

In Ch. 2 an overview is given on the challenges for future devices. Problems and limits of scaling are summarized. It turns out that besides their increased performance, traditional technologies for logic and memory devices still possess principle disadvantages. Some prominent examples for alternative technologies indicate the problems of conventional technologies in the future. The technological relevance of spin valves is explained afterwards. In contrast to other technologies spin valves allow for a functional diversification. That means one device can be used for many different applications. The state of the art of memory and logic devices is recapitulated along with the physics of spin valves. Finally, the modeling of spin valves is reviewed with emphasis on compact models. It is motivated why two new approaches for a compact are still necessary.

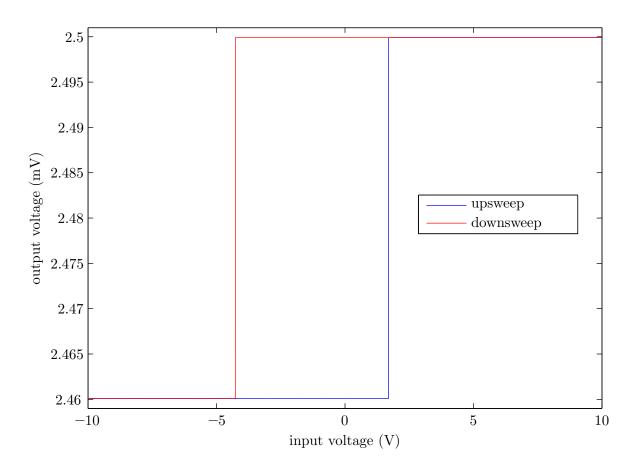

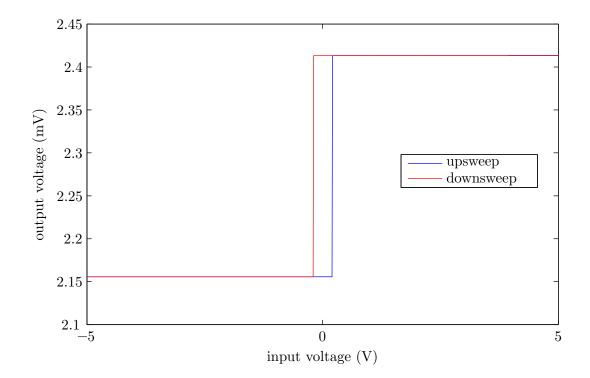

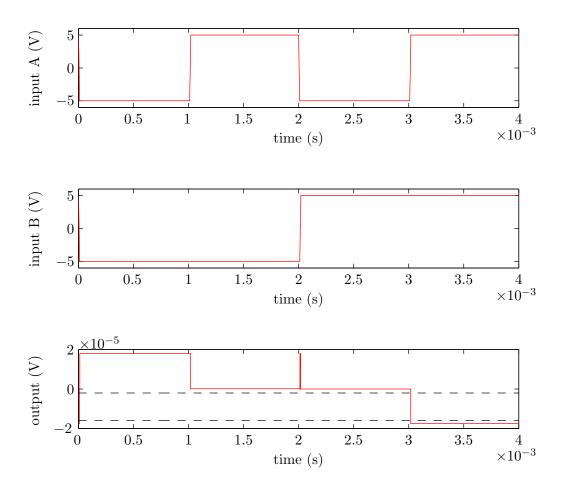

Two different equivalent electrical circuits are described in Ch. 3. The first circuit performs a rectangular-shaped hysteresis that approximates the electrical resistance of spin valve. The dimensioning of the circuit is shown in two case studies, first for a spin valve with a small difference between parallel and antiparallel configuration and second for a spin valve with a large difference between low and high resistance. The values are guided by experimental studies of spin valves. Picking up both case studies again, the feasibility of logic gates with the equivalent circuit is evaluated.

The second equivalent circuit allows mimicking the hysteresis at a tunable accuracy. In contrast to the first circuit, this circuit models a spin valve as a device with two terminals. The feasibility of logic gates using this circuit is discussed.

The conclusion and the outlook on possible future work are presented in Ch. 4.

The netlists of the circuits related to the first equivalent circuit (with a rectangular-shaped hysteresis) and those for the second circuit (with a realistic hysteresis) can be found in the appendix.

### Chapter 2

### **Fundamentals**

In this thesis the feasibility of logic gates and memory devices based on spin valves is investigated and evaluated. The transistor was invented in order to improve the switching speed and the reliability of electronic systems. In analogy to this development, spin valves are promising candidates for future logic gates and memory devices. For the design of systems based on spin valves an application-oriented modeling approach is necessary. A compact model for spin valves that captures all relevant electrical properties at a reasonable complexity is essential for system design. After an overview of the historical developments, in this chapter the challenges for future devices are identified. A reasonable example shows a fundamental limit for the miniaturization of devices. An overview on the technological relevance of spin valves is given afterwards. Because spin valves possess some fundamental advantages over traditional technologies, the underlying physics are outlined. Finally the state of the art of compact models for spin valves is summarized and reviewed as the basis for the results in the next chapter.

#### 2.1 Historical development

By the middle of the 1940's the main components of electronic circuits were passive devices, like resistors, inductors, and capacitors as well as active components like vacuum tubes and relays [6,7]. A complex system at that time was the electronic controller of the B-29 aircraft which consisted of about 300 vacuum tubes. The ENIAC, one of the fastest computers back then, consisted of over 17,000 tubes and weighted approximately 30,000 kg [8,9]. The first program-controlled digital computer, Konrad Zuse's Z3 from 1941 had used up to 2400 relays. On the Z3 an addition operation of two numbers takes in average 0.8 s at a clock frequency of approximately 5.3 Hz [10]. In the 1940's scientists at the Bell Laboratories in Murray Hill, New Jersey were looking for an analog of the fast, but unreliable vacuum tube and the slow electromagnetic relay. The result of their work was the invention of the bipolar transistor in 1948. In contrast, the actual analog to the vacuum tube, the field-effect transistor was proposed already in 1926, but it would not fabricated before 1952 [11–13]. Kilby and Noyce independently from each other invented the integrated circuit in 1958 based on bipolar transistors. The inventions of this era led to an enormous improvement of the reliability

and the speed of computations [6,8]. In 1965 Gordon Moore, director of the research and development laboratories of Fairchild Semiconductor, published an article on his observation that the number of components in an integrated circuit at minimum costs roughly doubled every year [14]. By 1975 Moore, meanwhile one of the founders of Intel Corporation, himself adopted his statement to the recent developments. He now estimated that the number of transistors would double approximately every two years [15]. Eventually Moore's observation became known as "Moore's law". Up to now there has been an enormous development. Intel's 4004 microprocessor from 1971 consisted of 2,250 transistors; one of Intel's recent dual core Itanium 2 server chips has deployed 1.72 billion transistors [16].

#### 2.2 Challenges for future devices

Moore's law is an empirical observation that allows estimating the possible increase of devices on a given area. Miniaturization is one important requirement to speed-up calculations. Without the enormous miniaturization today's mobile phones, portable computers, and supercomputers would probably not exist at this performance or look totally different. The semiconductor industry has become a multi-billion dollar business. According to a recent press release of the European Semiconductor Industry Association the worldwide sales in 2009 for semiconductor devices were US\$ 226.313 billion [1]. The improvement of devices is generally referred to as scaling. Scaling of devices has become an important driver in semiconductor sales. Innovation is required to maintain the growth in this area. Basically, there are two ways of achieving innovation in the field of semiconductor-based computers (1) with improvements of the architecture and (2) with improvements of the fabrication technology and consequently the scaling of devices.

Some of the most important drawbacks of the classical von-Neumann computer architecture are:

- The sequential execution of instructions in spite of pipelining.

- The fetch phase in each execution of an instruction, even if the same instruction is executed many time in a row.

- The separation of the processor from the main memory. If the throughput of data between memory and processor is smaller than the rate at which data is processed, the processor has got to wait until data is available again. This problem is known as von-Neumann bottleneck. The problem gets worse with the ever increasing clock rates of modern processors.

There exists a wide variety of alternatives to the classical von-Neumann architecture. All aim at a higher performance by overcoming or weakening the principle drawbacks of the von-Neumann architecture. Some examples indicate this:

• Intel and other manufacturers have come up with multi-core processors. Instead of a single processing unit, two, four, eight or even more of them are available for parallel

execution. In the long run this strategy could be extended. Within its "Tera-scale Computing Program", Intel recently came up with an eighty-core processor. This processor could achieve 1.81 Tera-flops at a clock rate of 5.7 GHz [17].

- Scientists from the University of Texas at Austin, USA have proposed the TRIPS architecture<sup>1</sup> [18]. The authors have identified requirements for future computer architectures, such as power-efficient performance. A main characteristic of the TRIPS architecture is the direct instruction communication, where the hardware implements producer instructions whose output is directly available to consumer instructions, rather than writing the output to a register. A TRIPS machine offers an array of concurrently executing arithmetic logic units. By now, a TRIPS processor has been fabricated where a chip contains 170 million transistors spread over two processors [19].

- The Cell Broadband Engine is an architecture developed at IBM's research laboratories [20]. Instead of duplicating the same core on a chip, the Cell processor is a heterogeneous architecture. There is a mix of execution elements optimized for a range of applications. Applications are partitioned into components. Each component is executed on the most appropriate execution element. The Cell Broadband Engine consists of a 64 Bit processor and eight so-called synergistic processor elements, each with a local memory. Each processing unit is connected with a high performance bus.

- If the computer is designed for a single application only, its hardware can be optimized for this purpose. However, once the circuit is fabricated on a chip, it can no longer be modified. This type of computer is called an application-specific integrated circuit. It leads to a much better performance than a general-purpose processor or a domainspecific processor. From this point of view there arises a conflict between the flexibility of a general-purpose processor and the performance of an application-specific integrated circuit. Scientists like Hartenstein have proposed the approach of a reconfigurable computer that offers both, more performance than a general-purpose processor and more flexibility than an application-specific integrated circuit [21]. In a reconfigurable computer the hardware is configured for every task. The device structure will be reconfigured completely or in part depending on the succeeding task. Some years ago Hartenstein gave an overview on reconfigurable architectures in an influential paper [21]. An important requisite for a reconfigurable computer architecture is reconfigurable hardware, in particular field-programmable gate arrays. Spin valves overcome the drawbacks of conventional technologies like SRAM or Flash memory and are hence excellent candidates for field-programmable gate arrays.

The focus of this thesis lies in the evaluation of alternative technologies for logic gates and memory cells rather than in a profound review of the state-of-the-art of computer architecture. Besides improvements of the architectures of technical systems, improvements of the fabrication technology and consequently scaling of devices have led to an increase of their performance. Widely used technologies to implement memory cells are static random-access

<sup>&</sup>lt;sup>1</sup>TRIPS stands for "Tera-op[erations], Reliable, Intelligently adaptive Processing System"

memory (SRAM), dynamic random-access memory (DRAM), Flash memory, and magnetic hard-disks. An SRAM cell consists of two coupled inverters [22, 23]. Usually, an SRAM cell consists of six transistors, leading to a comparatively large cell area [24]. In a DRAM cell, the stored information is represented through the charge of a capacitor [25, 26]. The leakage current of the capacitor leads to a small retention time [24]. Flash memory is based on the so-called floating-gate transistor [27–29]. To alter the stored bit in a Flash cell, the electric charge within the floating gate has got to be changed by either injecting electrons into the floating gate or by removing electrons, respectively. These mechanisms limit the lifetime of the Flash cell. Main drawbacks of Flash memory are thus the long write/erase time and the small number of write cycles before the device will not work reliable anymore. The durability of a stored bit in a Flash cell is approximately 10<sup>9</sup> times worse than in an SRAM cell. The main drawback of hard-disks is their access time. These currently lie in the order of ms [30].

Scaling affects all aspects of a device, like the size, power consumption or clock frequency. The scaling of field-effect transistors (MOSFETs) led to a considerable increase of their switching speed [31]. An overview of the current state of the art in device scaling is given by the International Technology Roadmap for Semiconductors (ITRS) [32]. The Roadmap is sponsored by industry associations, like the Semiconductor Industry Association or the Japan Electronics and Information Technology Industries Association. Groups of experts work on different topics related with the semiconductor industry in order to collect recent characteristics of semiconductor devices. The ITRS aims at enabling technology assessment and is a reliable source of data. The recent edition of ITRS is that of 2009 [32]. The ITRS also gives an estimate on the scalability of devices, like a DRAM or a Flash memory cell. For DRAM cells the scaling is expressed for example through the half pitch which is half of the distance between two neighboring cells. It is projected that by 2024 the half pitch for DRAM will be at 8.9 nm [33]. Furthermore the ITRS names requirements that future devices should match. The drawbacks of the aforementioned technologies can be weakened through scaling. The area required for an SRAM cell would shrink for example if the size of the transistors would could be reduced. With miniaturization however manufacturers have to face problems in the following areas:

- leakage currents [34–40]

- thermal dissipation [35, 36, 40-42]

- power efficiency [36, 37, 43–45]

- reliability / statistical variability [9, 34–36, 39, 42, 45, 46]

- energy per bit [47]

- cost [40]

- lithography [9, 35, 40]

- delays on interconnections [48, 49]

With the miniaturization the quantum nature of the electrons becomes more and more dominant within the semiconductor transistors. Powell argues that Heisenberg's uncertainty relation defines the limit to miniaturization [35]. A more reasonable minimum scale of length in a solid is defined by the Fermi wavelength  $\lambda_F$ . The highest energy level for free electrons in a solid in the ground state is the Fermi energy. It is the energy on the surface of a sphere with radius  $k_F$ . The Fermi wavelength can be calculated from  $k_F = 2\pi/\lambda_F$ ; for copper  $\lambda_F = 4.6199 \cdot 10^{-10}$  m [50]. Powell's formulation of Moore's law yields that miniaturization converges to the Fermi wavelength for copper by 2021. For the calculation the 45 nm-technology node of 2008 was assumed. The lattice constant for silicon could be considered as another comprehensible estimate for the limits of miniaturization. The lattice constant of silicon is 5.43 nm [50].

The transistor was invented in order to improve the reliability and switching speed in electronic circuits. It allowed furthermore increasing the number of components in a circuit, that is, the complexity of the circuit. Along with the miniaturization of transistors came an increase of their performance. It seems likely that the enormous growth rates of the semiconductor industry could be maintained if further miniaturization would be possible. Miniaturization though becomes more and more complicated and researchers have identified fundamental limits as shown above. In spite of the improvements due to miniaturization, today's dominating technologies for memory devices show fundamental drawbacks. From a principle point of view, an ideal memory cell would be simple in its assembly, as it would consist of one device only. The data would be stored nonvolatile with a high data retention time and a small access time. The cell would show almost no material fatigue and would work with a low operating voltage. If it is possible to build up logic gates with the same device that is used for memory cells, this opens up new possibilities for reconfigurable computing devices. The number of gates or the size of a memory block could be freely allocable within the total number of devices. Functional diversification is identified to be one important challenge for future devices in the ITRS ("Moore's Law and More") [33]. It means that one device can perform different functionalities. There exists a wide variety of alternative technologies to implement memory cells. In the chapter on emerging research devices of the ITRS [51] several emerging memory technologies are named with demonstrated and projected parameters. Among these memory technologies are current-driven spin valves. Other promising technologies for example are:

• Ferroelectric random-access memory cells (FeRAM). The FeRAM cell consists of a capacitor with a ferroelectric layer as the dielectric and a pass transistor; thus the structure is similar to a DRAM cell. A voltage pulse is applied to set the electric polarization of the ferroelectric layer. Binary states can be distinguished through the charge of the ferroelectric capacitor [52]. Data is readout by applying a voltage pulse, which subsequently requires reprogramming. Recently a 128 Mb FeRAM device was presented [53]. A read/write voltage of 220 mV was achieved at a cell size of 0.252 μm². The clock frequency was 400 MHz. Ferroelectric field-effect transistors on the other hand have a gate dielectric made of a ferroelectric material. FeFETs allow for a non-destructive read-out in contrast to ferroelectric capacitors, and show a better scalability due to their sim-

pler structure [54]. Takahashi *et al.* demonstrated a ferroelectric CMOS inverter [55]. FeRAM is a nonvolatile memory technology, because the ferroelectric polarization is conserved after programming.

- Carbon nanotubes. Carbon nanotubes (CNT) have gained attention because of their splendid electrical properties, such as a high carrier mobility [56]. A prominent example for a nanomechanical memory device is described by Rueckes et al. [57]. Here carbon nanotubes are used for both, the memory cells and the connections between them. A memory cell is based on a suspended matrix of nanotubes. Logic gates based on field-effect transistors with carbon nanotubes were fabricated by Bachtold et al. [58]. A field-effect transistor that employs a graphene quantum dot of 10 nm in width was recently demonstrated [59].

- Phase-change memory. The amorphous and crystalline state of a bulk material differ from each other. The optical contrast between both states is exploited in re-writable CDs and DVDs [60]. The phase change is induced by Joule heating in the device. The two different phases correspond to two different electrical resistances. The phase-change device is fabricated for example with a chalcogenide (e.g. sulfur, selenium, and tellurium) [61]. The crystalline phase has a low resistance (in the range of some  $k\Omega$ ), whereas the amorphous phase has a high resistance (in order of some  $M\Omega$ ). Phase-change memory is nonvolatile, shows a good scalability and performance and can be fabricated in a low-cost CMOS process [61].

- Molecular memories. Single molecules can be used as electronic switches and storage elements. The molecules can be tailored by chemical synthesis. Self-organizing molecules promise a high storage density [62]. Self-organizing devices could be used to cheaply achieve a high degree of parallelism for computations. Green et al. describe a 160 kbit molecular electronic memory circuit [63]. They could achieve 10<sup>11</sup> devices per cm<sup>2</sup>. According to Green et al. this is roughly the same density of devices projected for DRAM in 2020.

Besides these examples magnetic nanostructures also have gained attention, because they fulfill the requirements for ideal cells for memory and logic. In magnetic devices not only the charge of an electron is used to represent the state variable, but also the spin of the electron. This field of research is known as magnetoelectronics or more recently *spintronics* [64–66]; an early proposal on how the spin degree of freedom could be utilized in a device is the spin transistor by Datta and Das [67]. Ferromagnetic nanostructures also encounter challenges and limits. Problems are due to quantum and temperature fluctuations [68]. The most prominent example is the *superparamagnetic effect*, which limits for example the size of magnetic grains in hard disks. There exists a critical size for the grains, which depends on the uniaxial anisotropy and the volume of the particle [69,70]. Below the critical size, the magnetization of a particle is not stable and is switched randomly due to thermal excitation. Common strategies to shift the superparamagnetic limit include materials with higher anisotropy or the usage of single domain patterns [71].

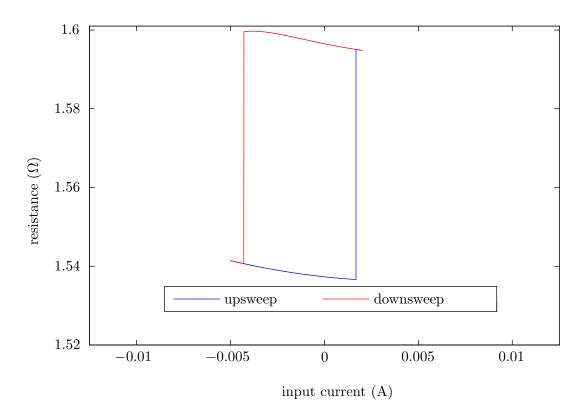

There is a variety of novel concepts for magnetic storage devices. Magnetic vortices and antivortices could be employed to constitute a memory cell [72,73] or logic gates [74]. Much attention is devoted to memory cells and logic gates based on magnetic domain walls [75,76]. S-shaped structures were lately proposed for logic gates [77]. Magnetic nanodots are also frequently proposed for logic devices [78,79]. Promising candidates for memory and logic devices are spin valves [80]. These are ferromagnetic devices in the nanometer scale whose electrical resistance can be changed either due to an applied magnetic field or an electrical current. Of particular interest for circuit design are the electrical properties of spin valves. Their behavior may be extracted from experimental data.

In this thesis models for the description of a spin valve's behavior are evaluated and two equivalent circuits are proposed. The circuits mimic its most important property, the electrical resistance. The resistance shows a hysteresis-like behavior; that means the electrical resistance does not depend on the input signal alone, but also on the previous configuration of the spin valve.

The key property of any ferromagnetic sample is its magnetization. The magnetization at each position in the sample can be regarded as a magnetic orientation just like in an array of tiny bar magnets. The orientation of the magnetization in one layer of the spin valve is fixed while the orientation of the magnetization in the other layer can be switched. The latter layer is called the free layer. With a spin valve binary symbols can be represented through the orientation of the magnetizations in the two ferromagnetic layers relative to each other, since both correspond to two different resistances. With the discovery of the giant magnetoresistance (GMR) effect, spin valves came into the focus of many scientists [66, 81, 82]. In 2007 Peter Grünberg and Albert Fert were awarded the Nobel Prize in Physics for this discovery [83]. Today's read heads in hard-disks are mostly GMR heads.

The decision whether spin valves are suited for computing devices depends on whether they achieve the features of today's semiconductor devices. Their ability of performing logical and storage operations is also important. The ITRS lists projected and demonstrated parameters of spin valves. They indicate the potential of spin valves in memory and logic devices. The most likely scenario is a combination of spin valves and MOSFET-based technologies, bringing together the assets of both worlds<sup>2</sup>. As mentioned above ("Moore's Law and More"), functional diversification is believed to be an important issue for future technologies for memory and logic devices. Spin valves allow for a diversification. It has been demonstrated that spin valves can be used for

- RF oscillators [84–86]

- biochips [87,88]

- logic devices in space applications (due to their radiation hardness) [89,90]

$<sup>^2 \</sup>rm MOSFET$  stands for metal-oxide-semiconductor field-effect transistor.

• sensors (e.g. read-head in hard-disks)

besides their use in logic and memory devices (cf. Sec. 2.3). Spin valves may overcome the memory hierarchy in computers [91]. The memory hierarchy describes the dichotomy between the cost and the performance of today's memory technologies. Hard-disks allow for a low cost storage, but show a large access time (see above). Technologies like SRAM have a small access time, but are too expensive for mass storage systems. The acceptability of spin valves also relies on the availability of models that allow simulations of large scale circuits, as a realistic and practical approach. In Sec. 2.5 the state of the art in modeling and simulation is described. In Ch. 3 two models of the spin valve's hysteresis are presented that allow for the simulation of complex systems based on spin valves.

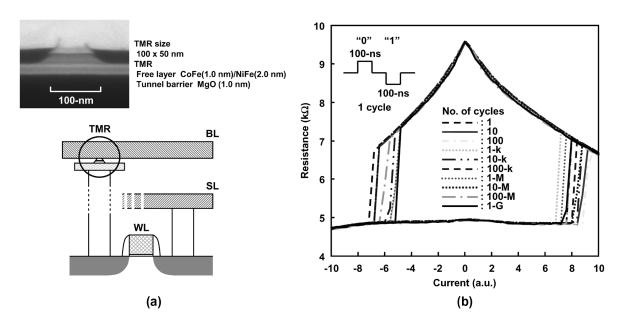

#### 2.3 Field-programmable gate arrays based on spin valves

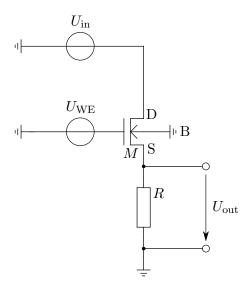

Spin valves can be used in combination with technologies based on the field-effect transistor to improve the features of a logic gate or a memory cell. For example, a field-effect transistor serves as a current source for the spin valve. According to the data from the ITRS spin valves already have comparable features with respect to SRAM, DRAM, and Flash memory or are expected to have [92]. Using spin-polarized currents helps reducing the current to write data [93]. A switching time of 100 ps was demonstrated with a current-driven MRAM cell [94], which is in the same order as the switching time for SRAM. Xu et al. depict a 256 Mb MRAM chip in 45 nm-process technology [95]. Another chip with current-driven MRAM exhibits a write time of 100 ns and a read time of 40 ns [96]. One proposal shows that the time to write a bit can be reduced to 2 ns [97]. In 2007 an MRAM chip was fabricated in a 28 nm-process resulting in a feature size of only 6  $F^2$  (compared to 45  $F^2$  for MRAM in the current ITRS) and a sensing current of approximately 10  $\mu$ A [98]. A clock frequency up to 500 MHz was demonstrated by Sakimura et al. [99]. There exists a number of works on memory modules based on field-driven spin valves [100–103].

At the 1960 International Solid-State Circuits Conference Proebster and Oguey proposed to use the magnetization in a Permalloy film as a memory cell and a logic gate [104]. The idea of implementing a logic gate with spin valves is propagated by several publications [64, 105, 106]. Today two different approaches are dominant. The first approach is to use a single spin valve. A Boolean input is represented through the direction (+ or -) of an electric current. For each input there is a separate wire connected to the spin valve. The currents on each line are summed up and the resulting Oersted field or spin-transfer torque switches the magnetization in the free layer (cf. Sec. 2.4). In between two sensing terminals the resistance of the spin valve is measured. The logical value 1 is represented through high resistance, that is, the antiparallel alignment of the magnetizations of both layers, and the logical 0 through low resistance which corresponds to a parallel alignment of the magnetizations of the layers. Similar to a memory cell, the input wires of the logic gate serve as the "bit-line"; the voltage between the sensing terminals is a selection signal like the one on a "word-line". Several works on logic gates based on spin valves follow this approach [107–111]. All relevant Boolean functions,

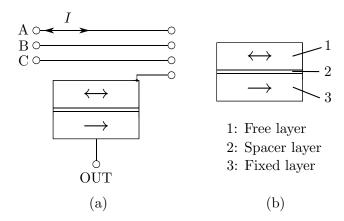

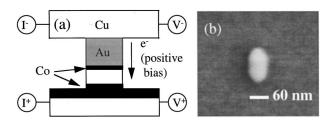

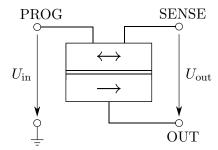

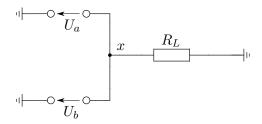

Figure 2.1: (a): Scheme of the logic gate based on a spin valve as introduced by Ney et al. [107]. On each of the input lines A and B a current can flow, each of equal magnitude. The direction of the current determines the orientation of the magnetization in the spin valve. Each of these currents,  $I_A$  and  $I_B$ , alone is not able to switch the magnetization in the free layer, only  $I_A + I_B$ . Together with  $I_A$  and  $I_B$ , a current  $I_C$  on the third input line C can switch the orientation of the magnetization in the fixed layer. This corresponds to programming the logic function of the gate. The output can be measured between an electrode attached to the top of the spin valve and the output terminal OUT. Originally Ney et al. assumed that the magnetizations are switched through Oersted fields which are generated through the currents on the input lines. (b): Layers of a spin valve.

like AND, OR, NAND, and NOR can be implemented. The concept is schematically shown in Fig. 2.1. Complex logic devices have been demonstrated following this concept [112,113].

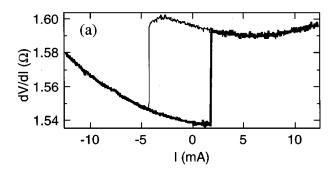

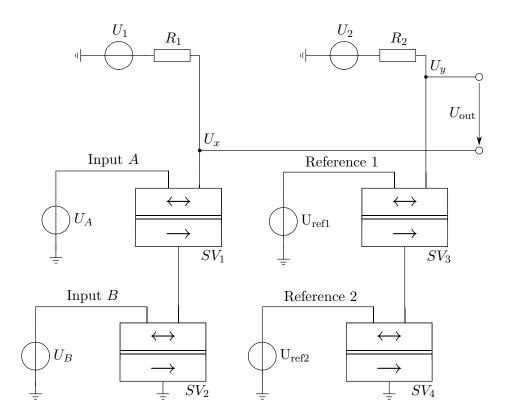

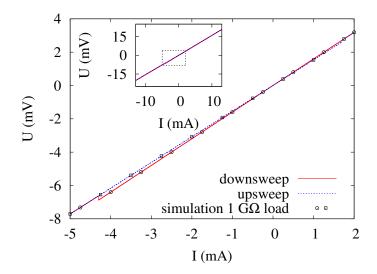

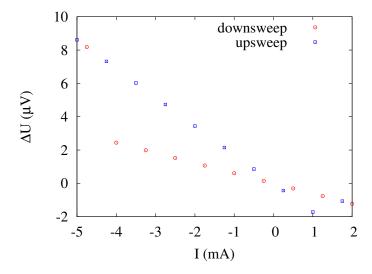

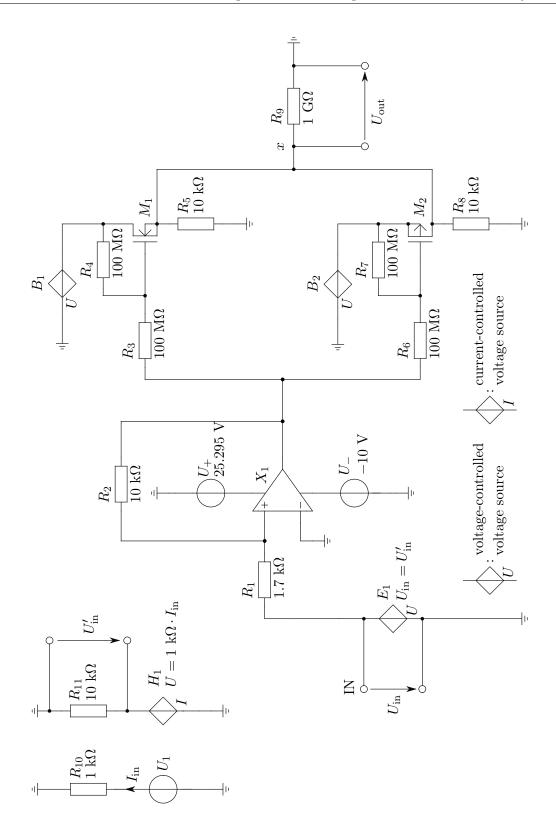

The second approach to implement logic gates was proposed by Richter et al. and uses four spin valves to implement a logic gate, forming an input and a reference branch [114–116]. Such a logic gate is shown in Fig. 2.2. The input branch is a series of two spin valves, whose resistance is determined or programmed by the two inputs. The reference branch also consists of two spin valves in series. Their resistance is determined before the gate can be used and remains unchanged during operation. In an experiment the difference between both states is measured to be of the order of  $2 \text{ k}\Omega$  [114]. A similar approach comparing the resistance of two branches was published by Hassoun et al. in 1997 [117]. Once the resistances of the spin valves are programmed, a sensing current is applied to both, the reference and the input branch. The resulting voltage drop between the input and the reference branch is the representation of the Boolean output of the gate. Similar to the first approach, a logical 1 is represented through high resistance which corresponds to an antiparallel alignment of the magnetizations relative to each other. A logical 0 is represented through low resistance. Proper operation of logic gates (NAND and NOR) has been demonstrated in experiments; special attention is given to the impact on the statistical variation of the magnetoresistance due to statistical variation during the fabrication and to the scalability of the devices [118–120]. In general the logic gates based on spin valves need additional amplification. The output voltage can

be in the range of mV only [114]. The output voltage of a logic gate however should be able to drive another gate. A simple solution is to use a comparator circuit: If the gate's output voltage is below an a priori chosen threshold, the output is converted to a convenient voltage to represent logical 0. Similarly the output of the gate is converted in order to comply with a desired voltage level for logical 1.

Richter et al. employ four spin valves for a single logic gate, whereas the logic gate of Ney et al. is constituted by a single spin valve only. The asset of Richter's gate however is that the authors experimentally prove proper operation of their logic gates taking into account also the influence of statistical variations of the fabrication. The problem of driving a number of other spin valves with the output signal of a spin valve is common to both concepts and needs to be solved.

The significance of spin valves as reconfigurable logic devices led to a multitude of publications on spin valves in field-programmable gate arrays (FPGA). An FPGA basically consists of an array of logic gates, programmable interconnections, input/output devices, and memory cells [121]. The logic gates are often implemented through memory cells as well as the interconnections [122]. With a number of inputs any combinational Boolean function can be mimicked with a memory cell. Such an addressable memory cell is often called a look-up table. They allow more flexibility than a rigid number of NAND and NOR gates. The idea of an FPGA is to directly configure the hardware depending on the specific application. A conventional FPGA is usually built with SRAM cells [122]. Computing with FPGAs combines the flexibility of a software-programmed computer and the performance of an application-specific integrated circuit [21, 123]. The term of a field-programmable logic gate in connection with spin valves can be traced back to 1997 [117]. This concept has been verified experimentally [124]. An influential work was published by Black et al. [106]. The authors performed simulations in SPICE of a flip-flop and could verify their design with an experimental study [125]. In the simulation the behavior of a spin valve was expressed in terms of an equivalent circuit that mimics measured characteristics like the hysteresis. Here an SRAM cell is coupled with several spin valves. Recent works show studies on look-up tables, either by experiment or simulation [126–128]. In some articles the design of a look-up table is discussed employing a so-called magnetic tunnel junction (MTJ). This is a spin valve where the spacer layer in between the ferromagnetic layers is an insulator [129–132]. Another approach is to express the resistance of the spin valve with two Ohmic resistors [89, 90, 133]. Look-up tables with magnetic tunnel junctions that utilize thermally assisted switching are also considered in the literature [134, 135].

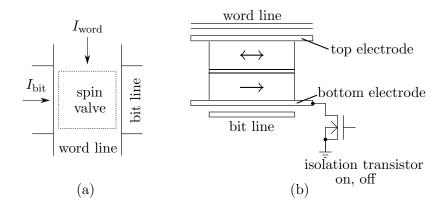

Figure 2.2: (a): Scheme of the logic gate based on spin valves as introduced by Richter et al. [114]. The input branch is the series of the two upper spin valves. Their resistance is determined, that is, programmed by the two inputs, A and B. The lower spin valves form the so-called reference branch. Their resistance is determined before the gate can be used and remains unchanged during operation. In the current configuration the gate is programmed as a NAND gate. If both reference cells are programmed to the antiparallel state, the gate performs the logical NOR function. A sensing current  $I_S$  is applied at the terminals SENSE2 and SENSE4. The current causes a voltage drop over the upper and lower branch. The current must be chosen such, that it does not alter the magnetization in the spin valve. The difference between the voltage drops in both branches is the output voltage of the gate. Attention must be paid to the situation where upper and lower branch have the same resistance. If deviations of the resistances due to the fabrication of the spin valves are neglected, the corresponding output voltage is 0V. In this case the gate is not be able to drive other gates. (b): The circuit symbol of the spin valve. The resistance of the spin valves can be measured when they form a voltage divider with an extra resistor, that is connected to the spin valve via the SENSE terminal. The output voltage that corresponds to the spin valve's resistance drops between the terminals SENSE and OUT. The terminal PROG indicates the input of the spin valve; a current is applied to switch the magnetization.

#### 2.4 Physics of spin valves

The ancient Greeks discovered that lodestone (magnetite) attracts iron. In those days lodestone was mined in the province of Magnesia. The physical phenomenon that causes the attraction of iron and lodestone is nowadays called *magnetism* [136]. Mattis explains that the term magnetism may also have originated from a shepherd called Magnes. The use of ferromagnetic material can be traced back to the forth millennium BC. Small tubular beads made of iron were found in Sumerian and Egyptian tombs; Chinese writings from this period also mention magnetite [137].

From hard disks it is well known that data is stored nonvolatile. A bit is stored within a small-sized region on a disk that is covered with a ferromagnetic film [138]. The orientation of such a region can be changed with a coil that is positioned above the region. A current through the coil generates a magnetic field which then determines the orientation of the region on the disk. In the absence of a magnetic field the orientation of the region is conserved. Similarly the electrical resistance of a spin valve remains unchanged until it is reprogrammed.

In the following the most important concepts related to the physics of spin valves are briefly described. Where necessary, further reading is suggested to the reader.

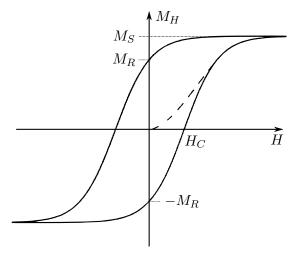

It is the ferromagnetic materials that are used in hard disks and magnetic nonvolatile memory cells. Ferromagnetism in a solid arises because of a spontaneous magnetic moment in the material that exists even when no external magnetic field is present. The magnetic moment is caused by the spin and the orbital angular momentum of the electrons in the solid. The magnetization is a vector that is defined as the magnetic moment per unit volume [50]. It is the most important quantity in the context of spintronic devices. The absolute value of the magnetization in a ferromagnet is sketched in Fig. 2.3; the hysteresis is an ambiguous function of the applied field. Well distinguishable states  $M_R$  and  $-M_R$  may represent logical values 0 and 1 in magnetic memory and logic devices. The total magnetic field in a ferromagnet does not only depend on an external magnetic field. The so-called effective field also has contributions from within the ferromagnet itself. The anisotropy field depends on the direction of the magnetization relative to the structural axis of the material. The exchange field is caused by the preference of a ferromagnet to have its magnetization aligned parallel. Ferromagnets have a stray field which also contributes to the effective field. The stray field can be made visible outside the ferromagnet for example by sprinkling iron filings around the ferromagnet. Eventually magneto-elastic interactions and magnetostriction have an influence on the effective field [139, 140]. An established model to describe the dynamics of the magnetization is the so-called Landau-Lifshitz-Gilbert equation [140–145]. In the micromagnetic model magneto-elastic interactions and magnetostriction are not included explicitly. The micromagnetic model allows to spatially resolve the magnetization dynamics of a spin valve. However, it is too generic from the application point of view. The simulation of a large array of spin valves using the micromagnetic model would be not manageable in a reasonable computation time. An intuitive approach to reduce the complexity of the micromagnetic model

Figure 2.3: Schematic representation of the magnetization in a ferromagnet depending on the applied magnetic field. The magnetization shows a hysteresis. H is the strength of the magnetic field,  $M_H$  is the magnetization in the direction of the applied magnetic field.  $H_C$  is the coercive field strength; this is the field strength, where  $M_H = 0$ . The remanence is defined as the magnetization at zero field. If the applied field is swept in positive direction, the remanence is  $M_R$ ; if the applied field is swept in the negative direction, the remanence is  $-M_R$ .  $M_S$  is the saturation magnetization, where apart from thermal excitation the magnetization is completely aligned in the direction of the applied field. If the sample is initially unmagnetized, the dashed curve is obtained during the sweep of the applied magnetic field; this curve is called initial magnetization curve. Sketch modified from reference [139].

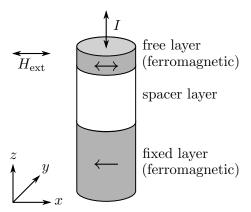

Figure 2.4: Sketch of a spin valve. The free and fixed layer are made of a ferromagnet. The spacer layer is either made of a non-magnetic metal or an oxide. The current I indicates current-induced switching. If it flows through the fixed layer first, this leads to a parallel orientation of the magnetization in the free layer with respect to the magnetization of the fixed layer; if the current flows through the free layer first an antiparallel orientation of the free layer is obtained.  $H_{\rm ext}$  indicates field-induced switching of the magnetization in the free layer. A parallel orientation of the magnetizations corresponds to a low resistance, whereas an antiparallel orientation corresponds to a high resistance. Both configurations can be used to represent logical values 0 and 1.

is to reduce the spatial and temporal resolution of the magnetization. The resulting model is called the *macrospin model*. Such a coarsening is crucial since it reduces the accuracy of the model with respect to the magnetization dynamics in spin valves [146]. The idea that a spin valve possesses only two configurations of the magnetization of the free layer (parallel or antiparallel to the magnetization of the fixed layer) is a reduced macrospin model. However, the micromagnetic model is not a compact model in terms of Verret's quality criteria for compact models.

Spin valves are devices in the range of some nanometers in size. They consist of at least two magnetic layers with a non-magnetic conducting or insulating layer, the spacer layer, in between. The thicknesses of the layers depend on the actual assembly of the spin valve. The thicknesses lie in the order of some nm [147]. The alignment of the magnetization in one layer is fixed due to a higher coercivity. The alignment of the magnetization in the other layer can be switched; in turn this layer is called the free layer. Figure 2.4 shows the sketch of a spin valve.

#### Magnetoresistance effects for spin valves

For circuit design two configurations of the orientation of the magnetizations with respect to each other are assumed, parallel and antiparallel. Both can be used to represent Boolean values. The state of the magnetization in the free layer can be detected with the help of the giant magnetoresistance effect (GMR) or the tunneling magnetoresistance effect (TMR). In the former case the spacer layer is made of a non-magnetic conducting material like copper. In the latter case the spacer layer is made of an insulator like magnesium oxide. The electrical resistance of a spin valve depends on the alignment of the magnetization in the free layer with regard to that of the fixed layer [148]. The resistance of a spin valve can be determined for instance by measuring the voltage drop due to a sensing current.

The GMR-effect was discovered by Grünberg and Fert [81,82]. The origin of the resistance is spin-dependent scattering within a ferromagnetic layer [148,149]: In Mott's two-channel model there exist two separate current channels for spin up and spin down electrons<sup>3</sup>. In a spin-polarized current the spin of a majority of electrons possesses one and the same orientation (e.g. spin up), whereas the spin of a minority of electrons possesses a different orientation. In one of the ferromagnetic layers of a spin valve majority electrons (with a spin parallel to magnetization in the layer) are almost not scattered, while minority electrons have a higher probability of being scattered.

An established model for the tunneling current through the spacer layer was proposed by Jullière who also performed experiments. A review on experiments and theory of tunneling magnetoresistance is given by Moodera and Mathon [2]. The spin of an electron is conserved during the tunneling. If the ferromagnetic layers are aligned in parallel, the tunneling probability is at highest and thus the tunneling current is at a maximum. This yields a low resistance. For the antiparallel orientation of the magnetizations in both layers, the tunneling probability and in turn the tunneling current is small. The antiparallel orientation corresponds to a high resistance.

The strength of the tunneling magnetoresistance and the giant magnetoresistance for a spin valve is usually expressed through

$$\frac{\Delta R}{R_P} = \frac{R_{AP} - R_P}{R_P},\tag{2.1}$$

where  $R_P$  is the (lower) electrical resistance for the parallel orientation of the magnetizations of the spin valve,  $R_{AP}$  is the (higher) electrical resistance of the spin valve for the antiparallel orientation of the magnetizations in free and fixed layer.

#### Mechanisms for switching the free layer

The most important mechanisms for switching the magnetization in the free layer are the field-induced, current-induced, and thermally assisted switching.

$<sup>^{3}</sup>$ The splitting of electrons into spin up and spin down electrons was first discovered by Gerlach and Stern [150]. The electron configuration for silver is  $4d^{10}5s$  [50].

#### Field-driven switching

Field-driven switching denotes the switching of the magnetization in the free layer by an applied magnetic field. It can be understood by looking at the relation between the magnetic flux density (also magnetic induction)  $\boldsymbol{B}$  (in  $\frac{\text{kg}}{\text{s} \cdot \text{A}}$ ), the magnetization  $\boldsymbol{M}$  and the magnetic field strength  $\boldsymbol{H}$  (both in A/m) [140]

$$\boldsymbol{B} = \mu_0 (\boldsymbol{H} + \boldsymbol{M}), \tag{2.2}$$

where  $\mu_0 = 4\pi \cdot 10^{-7} \frac{\text{kg} \cdot \text{m}}{\text{s}^2 \cdot \text{A}^2}$  is the magnetic permeability of free space [50]. By applying a magnetic field to a ferromagnet, the magnetization M is aligned in the direction H, like a compass is aligned in the direction of the earth's magnetic field. A steady current through a wire generates a magnetic field. A memory cell with a field-driven spin valve is normally assembled as shown in Fig. 2.5 [100, 151]. The word line is situated on top of the spin valve,

Figure 2.5: Sketch of a memory cell with a spin valve based on field-induced magnetization switching after Engel  $et\ al.$  and Slaughter [100, 151]. (a): Top view of the memory cell; the open borders of the write line and bit line indicate that the memory cells are arranged in a matrix.  $I_{\rm word}$  is the current across the word line and  $I_{\rm bit}$  the current across the bit line, respectively. (b): Assembly of the memory cell from the side. The isolation transistor controls the current from the top electrode to the bottom electrode. If the transistor is switched off, it possesses a high electrical resistance. It now prevents that a current on the word line can flow across the spin valve.

but not connected to the spin valve. The bit line lies underneath the spin valve, and is also not directly connected to the spin valve. The lower side of the spin valve is connected to a bottom electrode and its top face is connected to an electrode on top. The bottom electrode is connected to the drain of a field-effect transistor which controls if the spin valve is programmed (in other words if its resistance is changed or not). The transistor is called the *isolation transistor*. In the read mode the isolation transistor is switched on, which means a sensing current can flow from the word line to the isolation transistor. If the transistor is switched off, it possesses a high electrical resistance. It now prevents that a current on the word line can flow across the spin valve. For a reliable operation it is important that the resistance of the spin valves is not changed unintentionally. This implies a certain minimal

distance between adjacent cells at a specified current on word and bit line. Maffitt *et al.* review the design of field-driven spin valves in detail [152].

#### Current-driven switching

In 1996 Slonczewski predicted that a spin-polarized current changes the magnetization of a layer in the spin valve. Slonczewski assumed that the current flows perpendicularly to the ground plane of the spin valve, as indicated in Fig. 2.4 [153]. Electrons get spin-polarized when they traverse through the fixed layer. Their spin orientation depends on the magnetization in that layer. Electrons with spins that are aligned opposite to the localized spins in the fixed layer are reflected at the interface of that layer. A current traversing from the fixed layer to the free layer exerts a torque on the magnetization of the free layer that tends to align its magnetization parallel to the one of the fixed layer. On the other hand, a current flowing in the opposite direction causes an antiparallel alignment [66]. The torque of the itinerant electrons on the magnetization is called the spin-transfer torque (STT) in magnetic multilayers. The advantage of STT-driven spin valves would be an increase of the density of devices per unit area compared to field-driven spin valves. Now practically no magnetic field would be involved in switching the resistance of a spin valve. The mechanism has been observed in several experiments [147, 154].

For spin valves with a tunneling barrier between both ferromagnetic layers Slonczewski's theory is directly applicable. Parkin *et al.* explain however that the magnitude of the tunneling magnetoresistance effect is closely related to the degree of spin polarization of the tunneling electrons. The higher the spin polarization is, the higher the resistance change is [155]. Thus the situation where the spacer layer is a tunneling barrier is very similar to that where the spacer is a non-magnetic metal. Frequently the term spin-transfer torque is used also for spin valves with tunneling barriers [96].

#### Thermally assisted switching

If a ferromagnet is heated up above a material-dependent temperature, the so-called *Curie temperature*, the spontaneous magnetization in the sample vanishes [50]. The idea behind thermally assisted switching is to heat up the ferromagnetic layer that couples with an antiferromagnetic layer above a blocking temperature. In turn the orientation of the antiferromagnetic layer is set while cooling the layer to room temperature by applying a magnetic field. Prejbeanu *et al.* describe this mechanism in greater detail. They demonstrate that a current pulse of 500 ps was sufficient to switch the fixed layer [156].

#### 2.5 Modeling and simulation of spin valves

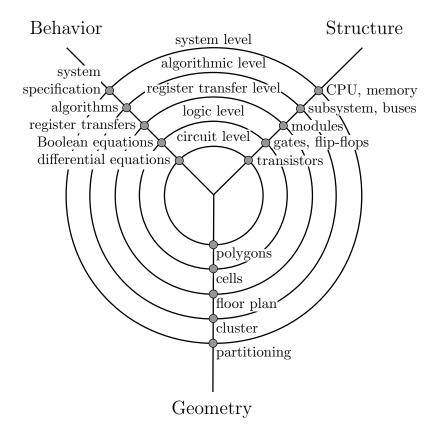

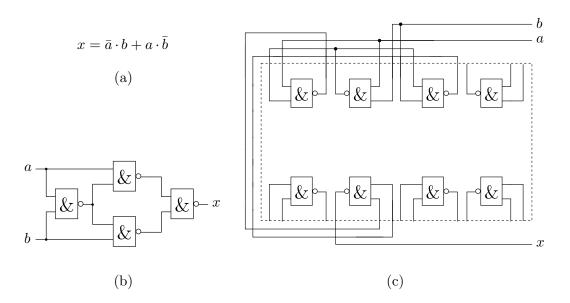

As described in Sec. 2.3, spin valves will become important for future computing systems. Over the years the complexity of computing systems has drastically been increased by their designers. Designs that consist of  $10^5$  up to  $10^7$  components are know as VLSI designs. VLSI stands for very-large scale integration [157]. To handle the complexity of a VLSI design Gajski and Kuhn proposed the so-called Y chart [158], which is shown in Fig. 2.6<sup>4</sup>. According to Gajski and Kuhn, a system can be described in three different domains, its behavioral representation, its structural representation, and its geometrical representation. All representations can be considered at different levels of abstraction. Each level is indicated by a concentrical circle in Fig. 2.6. In order to explain the different representations of a system, Gajski and Kuhn give the example of an XOR gate. If the inputs of the gate are denoted as a and b and the output as x, the XOR function is given as

$$x = \bar{a} \cdot b + a \cdot \bar{b}.$$

The representations are shown in Fig. 2.7. Similar flow charts between different levels of abstraction were proposed by various authors [160–163]. For each level of abstraction in the Y chart, there are tools available for system design. The higher the level of abstraction, the less detailed a system is described. This is particularly useful, because abstraction helps to cope with the complexity.

The basic level for the system design is the *circuit level*. The behavior of each component or device of the circuit is described by its electrical properties, that is, the U-I characteristic. The interplay between the components is expressed by Kirchhoff's laws [164]. The electrical properties of a component are expressed in terms of its model, more commonly referred to as the *device model*:

• The behavior of an Ohmic resistor in its simplest form is given in SPICE by

where XXXXXX is an alpha-numeric string for naming, n+ and n- are the element nodes, and finally value is the value of the electrical resistance in  $\Omega$ . In SPICE there is also a more sophisticated resistor model that allows for the calculation of the resistance based on geometric information and to be corrected for temperature [165]. Ohm's law  $R = U \cdot I$  describes the U - I characteristic of a resistor, where U is the applied voltage, and I is the current flowing through the resistor R.

• A plate capacitor is described by the model

$$C = \varepsilon_0 \cdot \varepsilon_r \cdot \frac{A}{d},$$

<sup>&</sup>lt;sup>4</sup>A recent processor from Intel consists of approximately 1.72 billion transistors [16]. This is an *ultra-large* scale integration (ULSI) design [159]. The universality of the Y chart though is not discussed in this work.

Figure 2.6: Y chart after Gajski and Kuhn [158]. A system can be described in three different domains, the behavioral representation, the structural representation, and the geometrical representation. The circles represent different levels of abstraction. The innermost circle represents the lowest level of abstraction and the outermost circle denotes the highest level of abstraction. The behavioral representation describes the functionality of the system, its inputs and outputs. Here it is important what the system is supposed to do, not how the functionality is achieved. The geometrical representation describes the geometry of the system; Of particular interest in this domain is where components are placed, e.g. a floor plan of the system or the wiring between the system's components. In the structural representation the structure of the system is described.

Figure 2.7: Example for the Y chart: different representations of an XOR function with two inputs. (a): a functional representation in terms of a Boolean equation, (b): a structural representation, and (c): a geometrical representation where every gate of the structural representation is assigned to a physical location. The dashed line indicates the housing of the respective integrated circuit.

where C is the capacitance in F,  $\varepsilon_0 = 8.8541 \cdot 10^{-12}$  F/m is the dielectric constant in vacuum,  $\varepsilon_r$  is the material-dependent dimensionless relative permittivity, A is the area of the plates in  $m^2$ , and d is the distance between the plates in m [166]. For a capacitor holds  $I = C \cdot \frac{dU}{dt}$ , where I is the current in A, U is the voltage over the capacitor in V, and t is the time in s [164].

• According to the Shockley equation, the forward current of a diode  $I_D$  can be calculated by

$$I_D = I_S \left( \exp\left(\frac{U_D}{U_T}\right) - 1 \right),$$

where  $I_S$  is the reverse bias saturation current,  $U_D$  is the voltage over the diode, and  $U_T = \frac{k_B \cdot T}{e}$  is the temperature voltage [167].  $k_B$  is the Boltzmann constant, T is the ambient temperature and e is the elementary charge.

The accuracy of the results with respect to experimental references essentially depends on the quality of the underlying model. It is clear that the Shockley equation cannot yield the most accurate and predictive results for the current through a diode. In this model the only difference between any two diodes is their reverse bias saturation current; the temperature voltage  $U_T$  only depends on the ambient temperature. For reliable results more complex models must be used that account for all relevant phenomena. On the other hand, a complex model may lead to time-consuming calculations. The trade-off between accuracy and the

complexity of the computation the model is a so-called *compact model* [168–171]. Verret identifies quality criteria for a compact model [172]:

- A quality model captures all relevant effects in the device. If available the results should match with experimental data.

- It is predictive at a sufficient accuracy. The model allows one to gain knowledge of the physics of the device.

- The model does not contain integrals, differentials or derivatives.

- A compact model should demonstrate a novel method or approach to increase the

efficiency of the simulation without loss of accuracy.

- The model provides new insights into the function, performance characteristics, or limits of conventional devices and ideally even suggests means of improvement for the device.

A well-known compact model for field-effect transistors is the Shichman-Hodges model. It is an equivalent circuit mimicking the U-I characteristics of a field-effect transistor based on the work of Ihantola and Moll [173, 174]. Ebers and Moll proposed an equivalent circuit mimicking a bipolar transistor [175]. In 2003 Laffont *et al.* published a compact model for Flash memory devices [176]. A compact model for a field-effect transistor made of carbon nanotubes was recently published by Frégonèse *et al.* [177].

In order to study the feasibility of spin valves in reconfigurable logic devices, what system designers need is a compact description of the behavior of a spin valve with emphasis on the electrical characteristics<sup>5</sup>. The magnetization dynamics of a spin valve is usually modeled by the micromagnetic model [141–145]. It allows to spatially resolve the dynamics of the magnetization in the free layer of a spin valve. In order to reduce the complexity, the spatial resolution can be reduced. The reduction results in the macrospin model. Here the dynamics in each layer is frozen out, such that it can be treated as one single spin. Such a coarsening is crucial since it reduces the accuracy of the micromagnetic model with respect to actual spin valves [146]. The validity of the macrospin model is still under debate. An important issue concerning the micromagnetic model is that not all relevant electrical properties of a spin valve, e.g. the electrical resistance of a spin valve, can directly be extracted from the simulation without additional calculations.

#### Compact models for spin valves – State of the art

The micromagnetic model is thus not the appropriate choice for simulating large arrays of spin valves. Instead, a compact description is required. In the literature two categories of compact models for spin valves are dominant. The first category of compact models can be denoted as *phenomenological models*. Their accuracy can be tuned to experimental reference data. The original spin valve is considered to be a black-box system; the origins of the spin

<sup>&</sup>lt;sup>5</sup>This includes spin valves in memory cells.

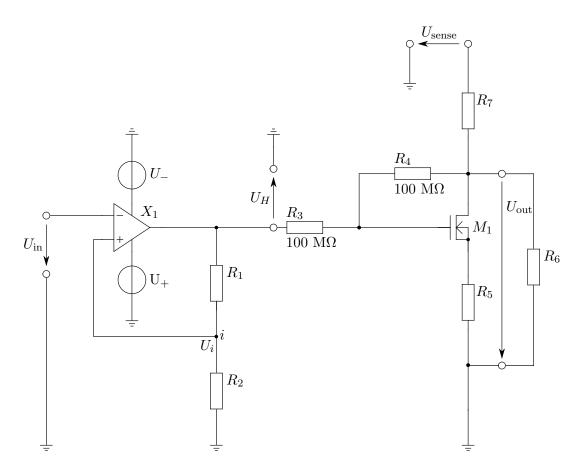

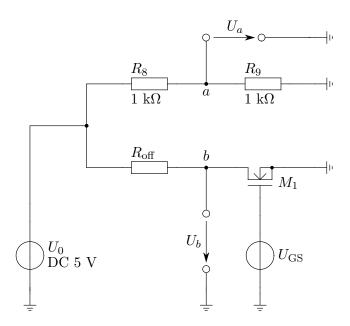

valve's behavior are unknown or irrelevant. In 1998 Das and Black proposed an electrical circuit mimicking the hysteresis of a spin valve using the commercial simulation program HSPICE [3,178]. This program is an electronics simulator. Based on experimental data, the hysteresis was expressed with a non-inverting Schmitt trigger and two piecewise linear voltage sources. The output voltage of the Schmitt trigger showed a rectangular-shaped hysteresis which attained two levels. The hysteresis was split into two branches, an upper and a lower branch. The actual output voltage was expressed through one of the piecewise linear voltage sources. Subsequently, the authors extended the functionality of their circuit by modeling the thermal behavior of a spin valve [179]. Das and Black employed an ideal operational amplifier in their circuit. There are two advantages of also using an electronics simulator:

- 1. It is quite convenient to include additional circuitry. A field-effect transistor could serve as a current source to switch the magnetization of the spin valve.

- 2. The hysteresis of a spin valve can plainly be implemented with an electric circuit, the Schmitt trigger (cf. Ch. 3).

Among many different tools for circuit simulation, the simulator SPICE is probably the best-known program for this purpose [180]. There are incompatibilities between different versions or spin-offs of SPICE. Das and Black used HSPICE's ideal operational amplifier for their circuit; in HSPICE the identifier for this device is "E". In SPICE an idealized operational amplifier does not even exist; here this identifier stands for linear voltage-controlled voltage sources [165, 180]. Furthermore SPICE lacks of controllable resistors which have been used by Das and Black in their circuit.

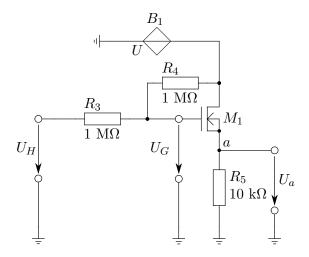

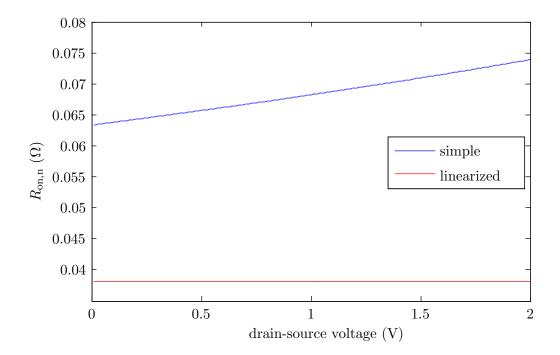

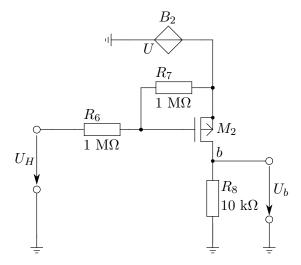

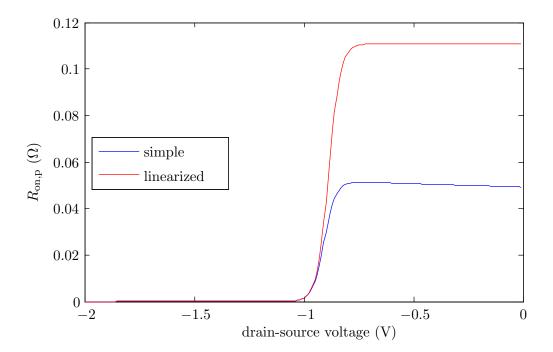

The problem of incompatibility between different simulation programs occurs if the circuit is modeled with devices that are not common to each program involved. It can be overcome by remodeling the respective devices or components with devices that are common to both programs. A new design is justified though if using it further reduces the complexity of the design. Depending on the application, it might be sufficient to model the resistance of a spin valve simply by Ohmic resistors or in combination with capacitors [181–183]. In 2005 Lee et al. proposed an equivalent circuit tailored to magnetic tunnel junctions which incorporates the temperature dependence of the hysteresis curve and the Stoner-Wohlfarth asteroid curve. The hysteresis of that circuit is assumed to be rectangular-shaped [4]. Recently the authors published an extended version of the circuit. They calculated a fitting function for the high-resistance state of the respective spin valve; the resistance in the low-resistance state was assumed to be constant [184]. Using models of real operational amplifiers leads to the problem that the simulation might not converge. The matter of convergence of a simulation within an electrical circuit for spin valves was recently addressed by Mukherjee and Kurinec [5]. Using realistic models of real devices, especially operational amplifiers, means that the spin-valve circuit inherits the characteristics of the devices used. This affects for example the range of the input signal for the spin valve; for details cf. Sec. 3.1.

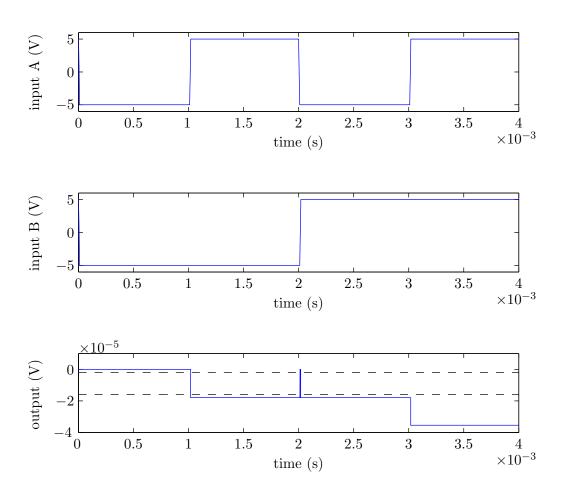

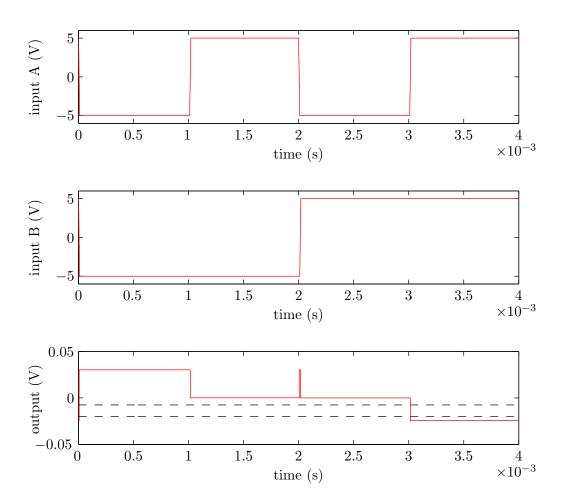

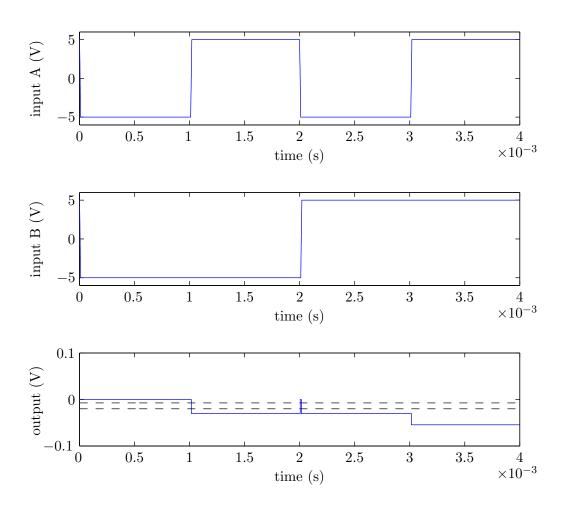

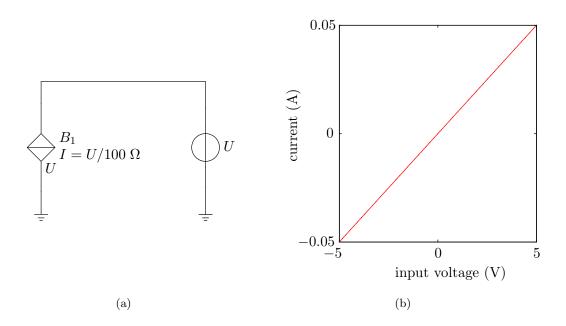

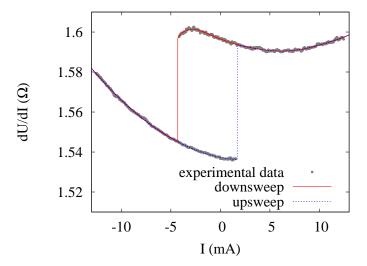

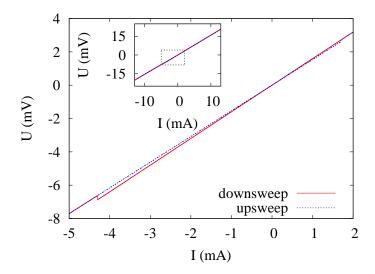

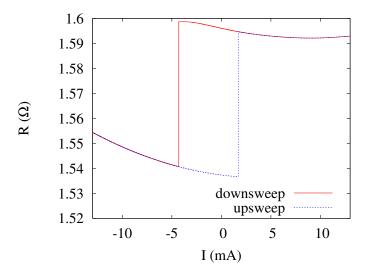

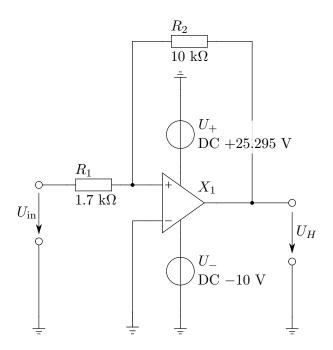

Besides equivalent circuits that mimic the behavior, there is another category of compact